Maxim Verbitskiy

FPGA designer/ Design Verificator

36 years old

Driving License

Minsk (220019) Belarus

Employed

Open to opportunities

Software Engineer (Design Verificator)

Softeq Flash Solutions

Since August 2015

- Design verification with UVM (SystemVerilog) - PCIe (Gen3, Gen4) block level verification, APB periferals block level verification, design-specific subblocks verification

- VCS simulator

Engineer (FPGA designer)

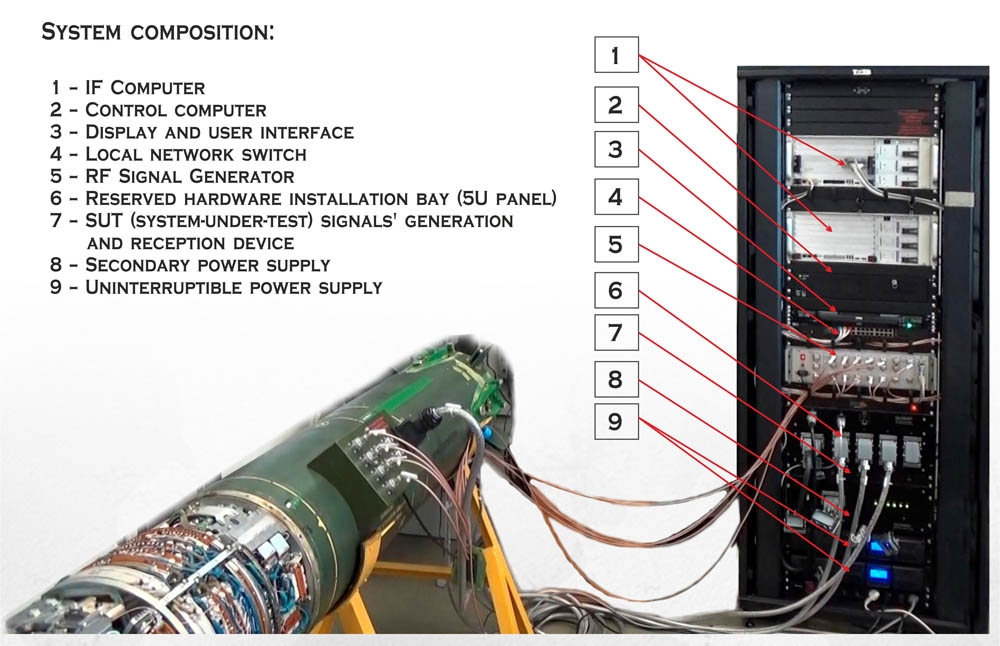

OPEN JOINT STOCK COMPANY "KB RADAR" - MANAGING COMPANY OF THE "RADAR SYSTEMS" HOLDING

August 2010

to August 2015

Full-time

Minsk

Belarus

- FPGA design (RTL design, functional simulation) - mostly with Intel (Altera) FPGA's, minor expirience with Xilinx FPGA's

- DSP algorithms implementation and testing (with Matlab, in FPGA's)

- Analog and digital circuits design (Altium Designer)

- Digital circuits testing with measurment equipment

- C/C++ programming (API creation for QNX RTOS, Drivers development for Windows with Jungo WinDriver)

Radioelectronic systems

-

RTL design

Advanced

-

Functional simulation

Advanced

-

Synthesis

Advanced

-

Timing analysis

Good

-

UVM

Advanced

-

Matlab

Good

-

FPGA

Advanced

-

Altium Designer

Good

-

Work with measurment equipment

Good

-

C/C++

Intermediate